### Features

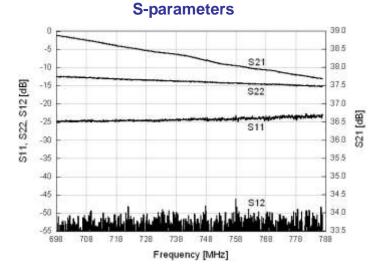

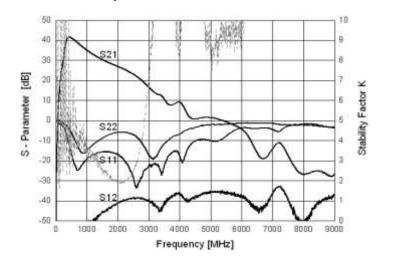

- S<sub>21</sub> = 37.6 dB @ 698 MHz

= 36.4 dB @ 787 MHz

- NF of 0.65 dB over Frequency

- · Unconditionally Stable

- $\cdot~$  Single 5V Supply

- · High OIP3 @ Low Current

### Description

The plerow<sup>TM</sup> ALN-series is the compactly designed surface-mount module for the use of the LNA with or without the following gain blocks in the infrastructure equipment of the mobile wireless (CDMA, GSM, PCS, PHS, WCDMA, DMB, WLAN, WiBro, WiMAX), GPS, satellite communication terminals, CATV and so on. It has an exceptional performance of low noise figure, high gain, high OIP3, and low bias current. The stability factor is always kept more than unity over the application band in order to ensure its unconditionally stable implementation to the application system environment. The surface-mount module package including the completed matching circuit and other components necessary just in case allows very simple and convenient implementation onto the system board in mass production level.

# **Specifications (in Production)**

Typ. @ T = 25°C, V\_s = 5 V, Freq. = 742.5 MHz,  $Z_{o.sys}$  = 50 ohm

| Parameter           | Unit | Specifications                   |       |           |  |

|---------------------|------|----------------------------------|-------|-----------|--|

| Parameter           | Unit | Min                              | Тур   | Max       |  |

| Frequency Range     | MHz  | 698                              |       | 787       |  |

| Gain                | dB   | 36                               | 37    |           |  |

| Gain Flatness       | dB   |                                  | ± 0.6 | ± 0.8     |  |

| Noise Figure (NF)   | dB   |                                  | 0.65  | 0.70      |  |

| Output IP3 (1)      | dBm  | 34                               | 35    |           |  |

| S11 / S22 (2)       | dB   |                                  |       | -18 / -10 |  |

| Output P1dB         | dBm  | 20                               | 21    |           |  |

| Switching Time (3)  | μsec |                                  |       |           |  |

| Supply Current      | mA   |                                  | 110   | 130       |  |

| Supply Voltage      | V    |                                  | 5     |           |  |

| Impedance           | Ω    |                                  | 50    |           |  |

| Package Type & Size | mm   | Surface Mount Type, 13Wx13Lx3.8H |       |           |  |

2-stage Single Type

### **More Information**

Website: www.asb.co.kr E-mail: sales@asb.co.kr

Tel: (82) 42-528-7223 Fax: (82) 42-528-7222

Operating temperature is -40°C to +85°C.

1) OIP3 is measured with two tones at an output power of 4 dBm / tone separated by 1 MHz.

2) S11/S22 (max) is the worst value within the frequency band.

3) Switching time means the time that takes for output power to get stabilized to its final level after switching DC voltage from 0 V to  $V_s$

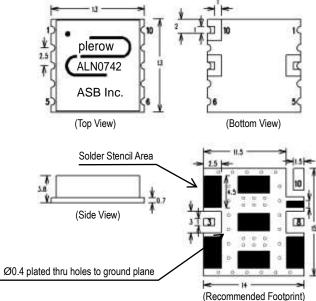

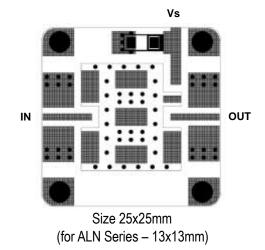

## Outline Drawing (Unit: mm)

| Pin Number | Function |  |  |

|------------|----------|--|--|

| 3          | RF In    |  |  |

| 8          | RF Out   |  |  |

| 10         | Vs       |  |  |

| Others     | Ground   |  |  |

|            |          |  |  |

Note: 1. The number and size of ground via holes in a circuit board is critical for thermal RF grounding considerations.

We recommend that the ground via holes be placed on the bottom of all ground pins for better RF and thermal performance, as shown in the drawing at the left side.

# Internally Matched LNA Module

# Noise Figure

S-parameters & K Factor

### OIP3

| Interno                   | <b>Ch Fr</b><br>od (T01) | eq 7 | 42,5 MHz               |      |                        |     |   | Iri                           | ig Free           |  |

|---------------------------|--------------------------|------|------------------------|------|------------------------|-----|---|-------------------------------|-------------------|--|

| Cent                      | ter 742                  | .500 | 0000 M                 | Hz   |                        |     |   | 240                           | 000 101           |  |

| Ref 4.3 dBm • Atten 32 dB |                          |      |                        |      |                        |     |   | Mkr1 742.000 MH:<br>4.066 dBm |                   |  |

| Samp<br>Log               |                          |      |                        | 1    |                        |     |   | -                             |                   |  |

| 18<br>dB/                 | -                        | -    | + 1                    | ţ—   |                        |     | - | 1                             | -                 |  |

| Offst<br>2.3<br>dB        |                          | L    |                        | 6    |                        | L   |   | -                             |                   |  |

|                           | 742.508 M                | Hz   | -1                     | 6W 3 | kHz.                   |     | 5 |                               | n 5 MHz<br>138 ms |  |

| TOI                       | (Worst C                 | ase) | 741.0 M                | Hz   | 35.69                  | dBm |   |                               |                   |  |

| TOI lower<br>TOI upper    |                          |      | 741.0 MHz<br>744.0 MHz |      | 35.69 dBm<br>36.85 dBm |     |   |                               |                   |  |

# Mk+1 660 MHz 8,562 dB 39,205 dB PKr3 742,55 MHz 8,484 dB 38,734 dB 9,800 Image: Start Start

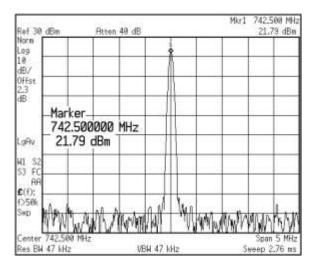

P1dB

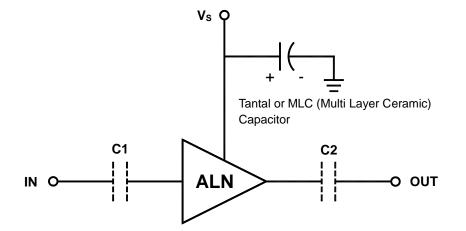

# **Application Circuit**

- The tantal or MLC (Multi Layer Ceramic) capacitor is optional and for bypassing the AC noise introduced from the DC supply. The capacitance value may be determined by customer's DC supply status. The capacitor should be placed as close as possible to V<sub>s</sub> pin and be connected directly to the ground plane for the best electrical performance.

- 2) DC blocking capacitors are always necessarily placed at the input and output port for allowing only the RF signal to pass and blocking the DC component in the signal. The DC blocking capacitors are included inside the ALN module. Therefore, C1 & C2 capacitors may not be necessary, but can be added just in case that the customer wants. The value of C1 & C2 is determined by considering the application frequency.

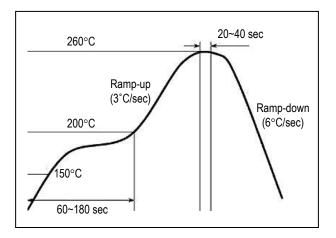

### **Recommended Soldering Reflow Process**

**Evaluation Board Layout**

Copyright ©2009-2017 ASB Inc. All rights reserved. Datasheet subject to change without notice. ASB assumes no responsibility for any errors which may appear in this datasheet. No part of the datasheet may be copied or reproduced in any form or by any means without the prior written consent of ASB.